프로그래밍

BOJ 1934 · 최소공배수

알고리즘 분류 : 수학 최소공배수는 유클리드 호제법을 이용하여 구현할 수 있다. 자세한 내용은 이곳을 참조. C++ 소스코드 #include int gcd(int x, int y) { while (y != 0) { int r = x%y; x = y; y = r; } return x; } int main() { int t, a, b; scanf("%d", &t); while (t--) { scanf("%d %d", &a, &b); printf("%d\n", (a*b)/gcd(a,b)); } return 0; } Python 3 소스코드 def gcd(x, y): while y is not 0: r = x%y x = y y = r return x for _ in range(int(input())): a, b..

BOJ 2609 · 최대공약수와 최소공배수

알고리즘 분류 : 수학 최대공약수(GCD; greatest common divisor)는 유클리드 호제법(Euclidean algorithm)을 이용하여 구현할 수 있다.r은 x를 y로 나눈 나머지 (r = x%y) GCD(x, y) = GCD(y, r) 를 r이 0이 될 때까지 반복적으로 수행r이 0일 때, y는 최대공약수이다. 최소공배수(LCM; least common multiple)는 미리 구한 최대공약수를 이용하여 구현할 수 있다.g = GCD(x, y)LCM = (x*y)/g C++ 소스코드 #include using namespace std; int gcd(int x, int y) { while (y != 0) { int r = x%y; x = y; y = r; } return x; } in..

Verilog HDL 모듈, 포트, 테스트벤치

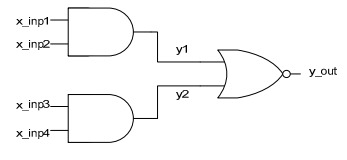

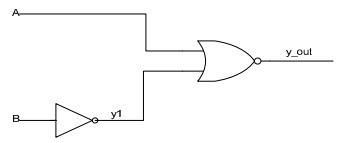

+ 모듈 (module) 베릴로그의 모듈은 C의 함수(function) 단위와 비슷하며, 베릴로그 설계를 위한 기본적인 블록 단위이다. module (포트 목록); 으로 시작하며, endmodule로 끝난다. 또한 하나의 모듈은 하나의 파일로 구성된다. 확장자는 .v 이다. * 예시 module example(inp1, inp2, inp3, inp4, result); input inp1, inp2, inp3, inp4; output result; wire t1, t2; and (t1, inp1, inp2); and (t2, inp3, inp4); nor (result, t1, 2t); endmodule + 포트 (port) 포트는 모듈과 모듈을 연결할 수 있는 인터페이스 이다. [범위] 의 형태로 선언하..

Verilog HDL 문법 (연산자, 데이터, 넷, 주석)

+ 연산자 (operator) 연산자는 산술 연산자, 관계 연산자, 논리 연산자, 시프트 연산자 등이 있으며 값을 연산하는 것에 사용한다. 구분 연산자 의미 산술 연산자 + 덧셈 - 뺄셈 % 나머지 * 곱셈 / 나눗셈 관계 연산자 == 같다 != 같지 않다 > 크다 >= 크거나 같다 오른쪽 Shift >), 왼쪽 shift (

Verilog HDL 문법 (레지스터, 벡터, 배열, 파라미터, 문자열)

+ 레지스터 (register) 레지스터는 데이터를 저장하는데 사용하는 변수이다. 으로 사용한다. 키워드 정의 reg 일반적으로 사용하는 레지스터 real 실수 표현을 하는 레지스터 time 시뮬레이션 시간을 저장하는 레지스터 integer 정수 표현을 하는 레지스터, signed 형태 사용가능 * 예시 reg start; initial begin start = 1'b0; #10 start = 1'b1; end real pi; initial begin pi = 3.141592; end + 벡터 (vector) 벡터란 n비트 폭을 가진 하나의 원소를 말한다. net과 reg 데이터 타입은 여러개의 비트를 가진 벡터로 선언할 수 있다. [최상위 비트:최하위 비트] 으로 선언한다. [높은 수:낮은 수] 또는 ..

Verilog HDL 문법 (컴파일러 지시어, 조건문, 다중 분기, 반복문)

+ 컴파일러 지시어 ' 형식으로 사용한다. `define 과 `include 와 `timescale 이 있다. define은 텍스트 매크로를 정의하는 용도로 사용하며, `include는 다른 verilog 소스 파일을 현재 소스 파일에 추가하는 용도로 사용한다. 일반적으로 헤더파일을 포함시키는데 사용한다. `timescale 은 모듈의 참조 시간 단위를 지정한다. `timescale / 형식으로 사용하며, 시간 단위는 시간 측정 단위이며, 시간 정밀도는 시뮬레이션에서 반올림된 지연의 정확도를 나타낸다. * 예시 `define SIZE 10 // `SIZE 를 10으로 사용 `define END $stop // `END 를 $stop 으로 사용 `include headers.h `timescale 150n..

Verilog HDL 문법 (키워드, 식별자, 숫자)

+ Verilog HDL의 특징 및 규약 베릴로그는 전체적으로 C 문법과 유사한 편이다. 문자는 대문자와 소문자를 구별(case sensitive)하며, 키워드는 반드시 소문자로 사용해야한다. 한 문장은 반드시 세미콜론(;) 으로 끝난다. (begin, end 등은 예외) + 키워드 (Keyword) 언어 구조를 정의하기 위해 사전에 예약된 식별자를 말한다. 키워드는 변수(variable)나 식별자(identifier)로 사용하지 않도록 한다. 키워드들은 아래와 같으며, 일반적으로 컴파일러가 예약어들을 파란색으로 표시해줄 것이다. always and assign begin buf bufif0 bufif1 case casex casez cmos deassign default defparam disable ..